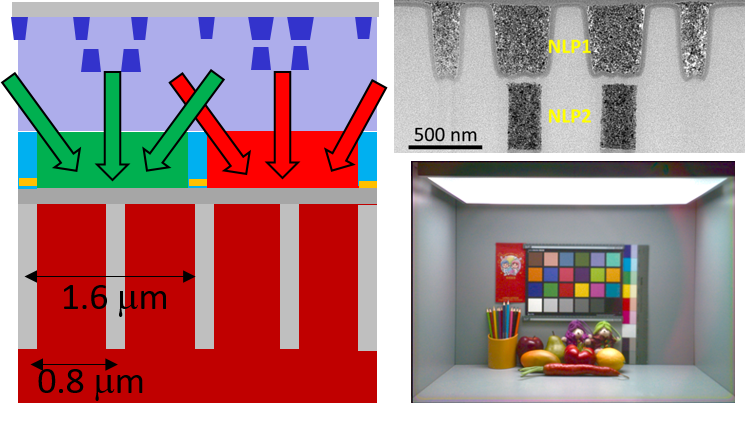

We demonstrated a die-level CMOS image sensor featuring 1.6 μm pixels and integrated nano-light pillars. This design achieved a 1.5 dB improvement in the signal-to-noise ratio (SNR). With an optimal pillar arrangement, the efficiency ratio between the die center and ide edge is comparable to conventional image sensors, while maintaining an acceptable Gr-Gb signal difference.

In this paper we present planar microlenses designed to improve the sensitivity of SPAD pixels. We designed diffractive and metasurface planar microlens structures based on rigorous optical simulations. The current melted microlens solution and designed diffractive microlens were implemented on STMicroelectronics 40nm CMOS testchips (32 × 32 SPAD array), and average gains of 1.9 and 1.4 in sensitivity respectively were measured, compared to a SPAD without microlens.