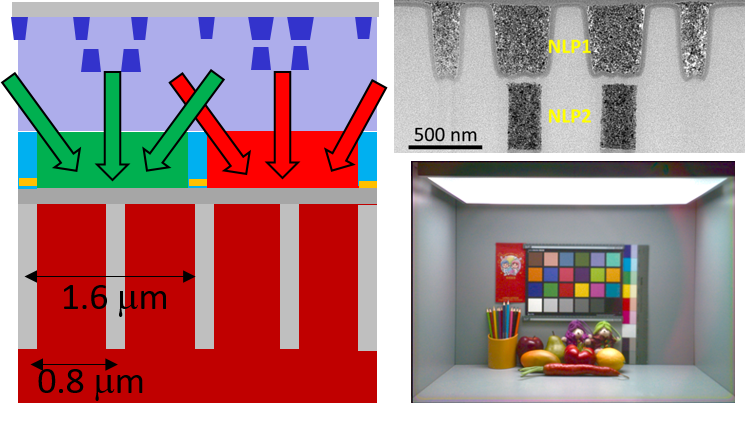

We demonstrated a die-level CMOS image sensor featuring 1.6 μm pixels and integrated nano-light pillars. This design achieved a 1.5 dB improvement in the signal-to-noise ratio (SNR). With an optimal pillar arrangement, the efficiency ratio between the die center and ide edge is comparable to conventional image sensors, while maintaining an acceptable Gr-Gb signal difference.

Chun-Yuan Wang, Chung-Hsuan Yu, Ken Chou, Yu-Shen Lu, Hao-Wei Liu, Jian Wen Luo, Shin-Hong Kuo, Yuchi Chang, Huang-Jen Chen, Po-Hsiang Wang, Peter Chiu, JB Lin, Chin-Chuan Hsieh, "Nano-light Pillar Structure Applied on 1.6 μm Pixel Size of CMOS Image Sensor for High Sensitivity" in Electronic Imaging, 2026, pp 292-1 - 292-6, https://doi.org/10.2352/EI.2026.38.6.ISS-292

Find this author on Google Scholar

Find this author on Google Scholar Find this author on PubMed

Find this author on PubMed