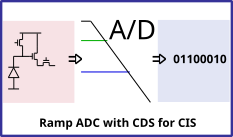

This article presents a novel architecture of a single slope single ramp column analogue-to-digital converter (ADC) for CMOS image sensors (CIS). The outlined ADC uses a global single slope ramp (SSR) with two comparators and two counters per column, one for the pixel reset level and one for the pixel signal level. A common reference level is used to start the conversion, while the reset and signal levels are used to terminate the respective conversion. With this architecture, the pixel reset, and signal levels are converted within a single conversion cycle. When the counter results are ready, a digital correlated double sampling (CDS) output is achieved by subtracting the reset counter value from the signal counter value with a digital subtractor. This architecture provides speed, offset compensation, and input swing adjustment through the reference level. Furthermore, the implementation is less vulnerable to temporal row noise, which is then suitable for low-noise applications. A 12-bit column ADC was designed and implemented in a 1920 x 1080 resolution CIS demonstrator, using a 0.18 m CIS process. With 200 MHz counter operation, the readout operation results in 25 frames per second.

Pedro Santos, Idham Hafizh, Jeffrey Prinzie, Paul Leroux, Guy Meynants, "Single Slope Single Ramp Column ADC with Digital CDS for CMOS Image Sensors" in Electronic Imaging, 2024, pp 282-1 - 282-5, https://doi.org/10.2352/EI.2024.36.7.ISS-282

Find this author on Google Scholar

Find this author on Google Scholar Find this author on PubMed

Find this author on PubMed