# The Simulation and Design of a Burst Mode 20Mfps Global Shutter High Conversion Gain CMOS Image Sensor in a Standard 180nm CMOS Image Sensor Process Using Sequential Transfer Gates

Xin Yue, Eric R. Fossum; Dartmouth College; Hanover, NH/USA

#### **Abstract**

A sequential transfer-gate and photodiode optimization method for CMOS image sensors is described in this paper. This technique enables the design of large-scale, ultra-high speed, burst mode CMOS image sensors (CIS) through a low-cost, standard CMOS image sensor process without the need for process customization or an advanced CIS process. Additionally, sequential transfer gates show a clear advantage by minimizing the floating diffusion capacitance and improving image sensor conversion gain in large-scale pixels. The simulation results further establish that full charge transfer can be achieved within 12ns for a 20µm test pixel.

#### Introduction

Ultra-high speed (UHS) image sensors are widely used in scientific and industrial applications to elucidate the UHS phenomena, such as high-energy X-ray imaging. In recent years, a few published papers have reported the frame rates of burst mode UHS image sensors in the range of millions of frames per second (Mfps) [1,8]. However, these published works required either an advanced process, for example, 110nm front-side-illuminated (FSI) or 130nm back-side-illuminated (BSI) charge-coupled-device (CCD) or a process specifically customized to design and fabricate UHS image sensors, as shown in Table 2. This research has been conducted after the outbreak of COVID-19 when access to advanced technology or a customized process is extremely challenging. Therefore, a design method has been implemented in this study to push beyond process limitations to achieve high-speed charge transfer and high conversion gain based on a standard 180nm process

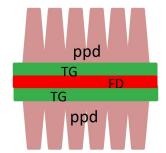

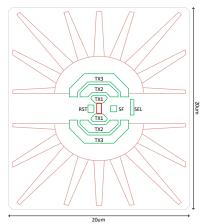

As [9] points out, there could be a few bandwidth bottlenecks in high-speed image sensor designs. However, for burst-mode image sensors, incident image information is first stored in in-pixel memories (sample and hold capacitors) and then read out from the memories slowly. Therefore, in-pixel circuit readout time is greatly reduced, and the pixel charge transfer time eventually dominates the burst mode image sensor frame rate. It is widely accepted [14] that quick charge transfer time can be achieved with a strong electric field. [10-11] analytically describe the relationships between electrostatic potential and photodiode width for small-size pixels (the short-photodiode effect). [12, 17] utilized the above effect and created an electric field along the electron transfer path in the photodiode to achieve fast charge transfer without process modification; however, for this photodiode design, the fill factor is limited. [13] extended the above idea to a multi-finger pixel and achieved about 50ns charge transfer time for large-scale pixels. However, due to a wide transfer gate and a large floating diffusion area, as is shown in Figure 1, this design suffered a low conversation gain and high capacitive transfer-gate loading. Technology computer-aided design (TCAD) simulation shows that for a 20µm pitch pixel, the pixel has a conversion gain (CG) less than  $10\mu\nu/e$ -(Figure 1).

To balance the recording length and frame rate for a burst mode image sensor, the capacitance of the in-pixel sample and hold capacitor is usually limited to a few tens of femtofarads (fF), for example, a 50fF per capacitor in [1]. The small capacitor's kT/C noise contributes significantly to the total input referred noise at the floating diffusion node with a small conversion gain. Based on the information reported, input referred noise is calculated to be 85eand 167e- for [7] and [8], respectively. [6] introduced a passive CDS amplifier to reduce the input-referred noise and reported the lowest state-of-art noise number at 8.4e-, as shown in Table 2. The gain of the passive CDS amplifier is determined by the capacitance ratio of the NMOS capacitor at depletion mode versus inversion mode, which is process and voltage dependent and introduces unavoidable non-linearity to the entire image sensor on the order of 3% [6]. Furthermore, the settling of the amplified voltage also limited the frame rate of the burst mode image sensor. Therefore, a processindependent method is needed to reduce the input-referred noise and to maintain the fast charge transfer and high frame rate.

## **Charge Transfer Time Optimization**

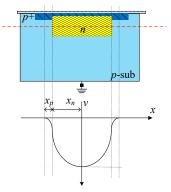

Figure 2 shows a simplified photodiode cross-section. Considering the short photodiode effect and applying the 1-D Poisson equation along the red dashed line, the maximum electrostatic potential in the photodiode is given by:

$$\psi_{max} \approx \frac{q.N_D \cdot X_n^2}{2 \cdot \varepsilon_0 \cdot \varepsilon_r} \left( 1 + \frac{N_D}{N_A} \right) \tag{1}$$

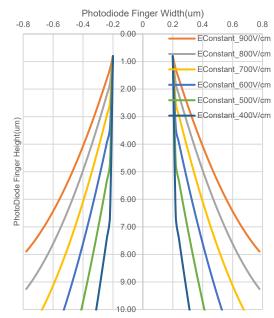

where  $\psi$  is the electrostatic potential in the photodiode, q is the elementary charge,  $N_D$  is the doping concentration of the photodiode, and  $N_A$  is the doping concentration of the substrate. Without modifying the doping concentration of the photodiode and substrate,  $X_n$ , the photodiode half width (half depletion width), is the only parameter to vary to form an electric field. Assuming the electric field is constant, the photodiode geometry shape is given by:

$$y = -\frac{q \cdot N_D \cdot X_n^2}{2 \cdot E \cdot \varepsilon_0 \cdot \varepsilon_r} \left( 1 + \frac{N_D}{N_A} \right) + C_0$$

(2)

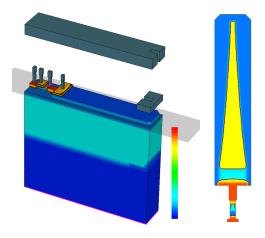

where y and  $X_n$  are the photodiode coordinates. Plugging in the process parameters and setting the electric field in the photodiode along the charge transfer direction varies from 400V/cm to 900V/cm, one can obtain different photodiode geometry shapes, as is plotted in Figure 3. Simple TCAD pixel models with different photodiode shapes are used to simulate electron transfer time, as Figure 4 shows. The metal shielding over the photodiode creates an aperture and forces incident light to only illuminate the tip of the photodiode so that photo-generated electrons will travel through the longest path in the photodiodes to the FD node. TCAD simulation results of the charge transfer time of different photodiodes are listed in Table 1. The EConstant\_800V/cm photodiode design is used in the proposed pixel design to balance the charge transfer time and fill factor tradeoff, as is displayed in Figure 5.

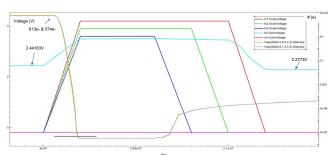

TX1, TX2, and TX3 in Figure 5 represent the three sequential transfer gates. Its operational timing is shown in Figure 6, where the red, green, blue, and cyan curves stand for the voltage of TX1, TX2, TX3, and floating diffusion, respectively. The yellow and gray represent the total number of electrons in the upper and lower photodiode. At the beginning of charge transfer, TX1, TX2, and TX3 all turn on simultaneously, where TX1's voltage is higher than TX2's, and TX2's voltage is higher than TX3's. At the end of the charge transfer, TX3 turns off first, followed by TX2, and eventually, by TX1. The TCAD transient simulation shows that charges can be fully transferred within 12 ns.

## **Conversion Gain and Noise Optimization**

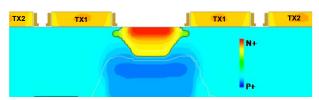

Compared to the baseline pixel in [13], the floating diffusion area in this design can be significantly decreased, as the Figure 5 red box shows. Additionally, unlike the traditional pixel, the proposed pixel does not directly transfer photoelectrons from the photodiode to the floating diffusion (FD) node. Therefore, it is safe to move the TX1 gate away from the floating diffusion node, as is illustrated in the cross-section in Figure 7, which effectively reduces the overlap capacitance between FD and TX1 gates and reduces dark current due to gate-induced-drain-leakage (DIGL) at floating diffusion node, and increases the conversion gain. The TCAD transient simulation in Figure 6 shows that conversion gain is calculated to be  $138\mu\nu/e$ -.

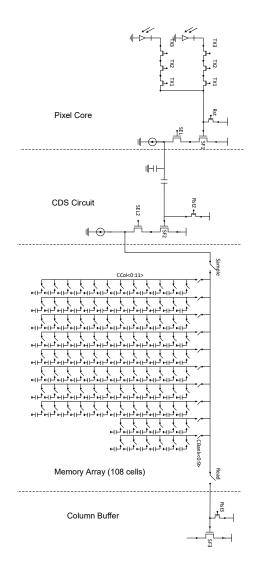

In order to further reduce the input-referred noise, a correlated-double-sampling (CDS) circuit is implemented in the pixel, as figure 7 shows, where the AC coupling cap between the first source-follower (SF) and second SF takes the voltage difference of pixel reset voltage and signal voltage and store it on the in-pixel sample and hold (S/H) capacitors. In total, 108 S/H capacitors were laid out in 52.8um pitch. The theoretical calculation and simulation yield only 5.6e- input referred noise is achieved at the FD node, much smaller than the 8.4e- noise reported in [6].

#### **Conclusions and Future Work**

A 20Mfps global-shutter burst mode CMOS image sensor with 5.6e- input-referred noise and 108 frame recording length was designed and simulated in a standard 180nm FSI process. By carefully optimizing the photodiode shape and introducing the sequential transfer gates, complete charge transfer was achieved within 12 ns. Additionally, the sequential transfer gate showed a clear advantage in minimizing the floating diffusion area, reducing the floating diffusion capacitance, and improving conversion gain. The sensor has been taped out, and sample dies are expected to return from the foundry in March 2023, with the characterization following receipt.

One of this design's applications is to enable the viewing of the dynamic response of materials under different stresses. Videos with millions of frames per second capturing the changes under a bright X-ray source will give an insight into the properties of the material under study, which may yield potential improvements to the material. This design is phase three of a series of projects. In phase one [16,18], we have demonstrated that the high energy X-ray (20-50Kev) quantum efficiency (QE) of a sensor designed in the same standard process can be increased by >10x with a Photon-Attenuation-Layer (PAL) deposited on top of the sensor. Therefore, the deposition of PAL onto this high-speed burst mode sensor will also be scheduled after the characterization.

#### References

[1] Suzuki, M., Sugama, Y., Kuroda, R., & Sugawa, S. (2020). Over 100 million frames per second 368 frames global shutter burst CMOS

- image sensor with pixel-wise trench capacitor memory array. Sensors, 20(4), 1086.

- [2] Tochigi, Y., Hanzawa, K., Kato, Y., Kuroda, R., Mutoh, H., Hirose, R., Tominaga, H., Takubo, K., Kondo, Y., & Sugawa, S. (2013). A global-shutter CMOS image sensor with readout speed of 1-tpixel/s burst and 780-mpixel/s continuous. *The IEEE Journal of Solid-State Circuits*, 48(1), 329–338.

- [3] Suzuki, M., Kuroda, R., Kumagai, Y., Chiba, A., Miura, N., Kuriyama, N., & Sugawa, S. (2016). An over 1Mfps global shutter CMOS image sensor with 480 frame storage using vertical analog memory integration. 2016 IEEE International Electron Devices Meeting.

- [4] Dao, V., Ngo, N., Nguyen, A., Morimoto, K., Shimonomura, K., Goetschalckx, P., Haspeslagh, L., De Moor, P., Takehara, K., & Etoh, T. (2018). An image signal accumulation multi-collection-gate image sensor operating at 25 Mfps with 32 × 32 pixels and 1220 in-pixel frame memory. *Sensors*, 18(9), 3112. <a href="https://doi.org/10.3390/s18093112">https://doi.org/10.3390/s18093112</a>

- [5] Etoh, T., Okinaka, T., Takano, Y., Takehara, K., Nakano, H., Shimonomura, K., Ando, T., Ngo, N., Kamakura, Y., Dao, V., Nguyen, A., Charbon, E., Zhang, C., De Moor, P., Goetschalckx, P., & Haspeslagh, L. (2019). Light-in-flight imaging by a silicon image sensor: Toward the theoretical highest frame rate. *Sensors*, 19(10), 2247. https://doi.org/10.3390/s19102247

- [6] Wu, L., San Segundo Bello, D., Coppejans, P., Craninckx, J., Süss, A., Rosmeulen, M., Wambacq, P., & Borremans, J. (2018). Analysis and design of a CMOS ultra-high-speed burst mode imager with insitu storage topology featuring in-pixel CDS amplification. *Sensors*, 18(11), 3683.

- [7] Kagawa, K., Horio, M., Pham, A.N., Ibrahim, T., Okihara, S., Furuhashi, T., Takasawa, T., Yasutomi, K., Kawahito, S., & Nagahara, H. (2022). A dual-mode 303-megaframes-per-second charge-domain time-compressive computational CMOS image sensor. *Sensors*, 22(5), 1953.

- [8] Mochizuki, F., Kagawa, K., Okihara, S., Seo, M.W., Zhang, B., Takasawa, T., Yasutomi, K., & Kawahito, S. (2016). Single-event transient imaging with an ultra-high-speed temporally compressive multi-aperture CMOS image sensor. *Optics Express*, 24(4), 4155. https://doi.org/10.1364/oe.24.004155

- [9] Suzuki, M., Kuroda, R., & Sugawa, S. (2018). A 125Mfps global shutter CMOS image sensor with burst correlated double sampling during photo-electrons collection. Extended Abstracts of the 2018 International Conference on Solid State Devices and Materials. https://doi.org/10.7567/ssdm.2018.j-6-05

- [10] Krymski, A., & Feklistov, K. (2005, June). "Estimates for Scaling of Pinned Photodiodes. IEEE Workshop on Charge-Coupled Devices and Advanced Image Sensors.

- [11] Park, S., & Uh, H. (2009). The effect of size on photodiode pinch-off voltage for small pixel CMOS image sensors. *Microelectronics Journal*, 40(1), 137-140. https://doi.org/10.1016/j.mejo.2008.06.071

- [12] Takeshita, H., Sawada, T., Iida, T., Yasutomi, K., & Kawahito, S. (2010). High-speed charge transfer pinned-photodiode for a CMOS time-of-flight range image sensor. SPIE Proceedings. https://doi.org/10.1117/12.846277

- [13] Cao, X., Gäbler, D., Lee, C., Ling, T.P., Jarau, D., Kho, D., Tien, C., Chuan, T., Bold, B. (2015). Design and Optimization of Large 4T Pixel. X-FAB Semiconductor Foundries AG, Erfurt, Germany.

- [14] P., T. A. J. (2011). Chapter 1 in Solid-state imaging with chargecoupled devices. Essay, Springer, 25-31.

- [15] Etoh, T. G., Poggemann, D., Kreider, G., Mutoh, H., Theuwissen, A. J. P., Ruckelshausen, A., Kondo, Y., Maruno, H., Takubo, K., Soya, H., Takehara, K., Okinaka, T., & Takano, Y. (2003). An image sensor which captures 100 consecutive frames at 1 000 000 frames/s. *IEEE Transactions on Electron Devices*, 50(1), 144–151. https://doi.org/10.1109/ted.2002.806474

- [16] Lee, E., Anagnost, K. M., Wang, Z., James, M. R., Fossum, E. R., & Liu, J. (2021, April 30). Monte Carlo Modeling and design of photon energy attenuation layers for >10× quantum yield enhancement in SI-based hard X-ray detectors. MDPI. Retrieved November 18, 2022, from https://www.mdpi.com/2410-390X/5/2/17

- [17] Liu, L., Yang, S., Yan, M., Li, B., Guo, Y., Guo, M., Li, G., & Zhou, E. (2023). The effect of photodiode shape on pinning potential for charge transfer in CMOS image sensors. *Microelectronics Journal*, 131, 105651. https://doi.org/10.1016/j.mejo.2022.105651

- [18] Z. Wang, K. Anagnost, C. W. Barnes, D. M. Dattelbaum, E. R. Fossum, E. Lee, J. Liu, J. J. Ma, W. Z. Meijer, W. Nie, C. M. Sweeney, A. C. Therrien, H. Tsai, and X. Yue, "Billion-pixel X-ray camera (bipc-X)," AIP Publishing, 01-Apr-2021. [Online]. Available: https://aip.scitation.org/doi/abs/10.1063/5.0043013. [Accessed: 22-Jan-2023].

## **Acknowledgments**

The authors are grateful to Jeph Wang and Bob Reinovsky from Los Alamos National Laboratory and Department of Energy for sponsoring this research (Contract No. 89233218CNA000001), Xuezhou Cao, Guang Yang, Jifeng Liu for discussion, and X-Fab for fabrication of this sensor.

## **Author Biography**

Xin Yue received his Bachelor of Science from the Wuhan University of Technology (2011) and his Master of Science from the University of Southern California (2013). He was employed as a staff mixed-signal circuit design engineer at Forza Silicon, CA, for 7 years. Currently, he is pursuing his Ph.D. in engineering sciences from Dartmouth College. His work predominantly focuses on ultrahigh speed, low noise, and advanced image sensor design.

## Figures and Tables

Figure 1. High speed pixel layout of [13]

Figure 2. A simplified pinned photodiode

Figure 3. Photodiode fingers with different electric field

Figure 4. TCAD model of sample pixel (right) and its cut-plane(left)

Figure 5. High speed pixel core layout

Figure 6. Transient TCAD simulation of charge transfer

$\textbf{\textit{Figure 7.} Cross-section of the low capacitance floating diffusion}$

Figure 8. High-speed high conversion gain pixel schematic

| Charge Transfer Time of Different Photodiodes |      |      |       |       |      |  |  |  |  |  |  |  |

|-----------------------------------------------|------|------|-------|-------|------|--|--|--|--|--|--|--|

| CTE                                           | 90%  | 99%  | 99.5% | 99.9% | Unit |  |  |  |  |  |  |  |

| Econstant_400                                 | 10.2 | 41.2 | 51.3  | 75.2  | ns   |  |  |  |  |  |  |  |

| Econstant_500                                 | 0.67 | 17.4 | 25.8  | 47.0  | ns   |  |  |  |  |  |  |  |

| Econstant_600                                 | 0.67 | 5.01 | 11.0  | 28.3  | ns   |  |  |  |  |  |  |  |

| Econstant_700                                 | 0.74 | 1.51 | 5.16  | 19.3  | ns   |  |  |  |  |  |  |  |

| Econstant_800                                 | 0.82 | 1.18 | 3.78  | 15.5  | ns   |  |  |  |  |  |  |  |

Table 1. Charge transfer time of different photodiode designs

| Performace Comparasion Between SOAs |                 |                              |               |               |              |                         |                      |               |            |  |  |  |

|-------------------------------------|-----------------|------------------------------|---------------|---------------|--------------|-------------------------|----------------------|---------------|------------|--|--|--|

| Ref                                 | Process<br>(nm) | Process<br>Customi<br>zation | Pixel<br>Size | CG<br>(uV/e-) | FWC<br>(Ke-) | Frame<br>Rate<br>(Mfps) | Recor<br>d<br>Length | Noise<br>(e-) | DR<br>(dB) |  |  |  |

| [1]<br>2019                         | 180 FSI         | Yes                          | 35*7<br>0     | 99            | 11           | 100                     | 368                  | N/R           | N/R        |  |  |  |

| [2]<br>2013                         | 180 FSI         | Yes                          | 32*3<br>2     | 74            | N/R          | 10                      | 128                  | N/R           | N/R        |  |  |  |

| [3]<br>2017                         | 180 FSI         | Yes                          | 32*3<br>2     | 112           | 10           | 10                      | 480                  | N/R           | N/R        |  |  |  |

| [4]<br>2018                         | 130 BSI<br>CCD  | Yes                          | 72.5*<br>72.5 | N/R           | N/R          | 25                      | 1220                 | N/R           | N/R        |  |  |  |

| [5]<br>2019                         | 130 BSI<br>CCD  | Yes                          | 12.7*<br>12.7 | N/R           | 7            | 100                     | 5                    | N/R           | N/R        |  |  |  |

| [6]<br>2018                         | 130 BSI         | N/R                          | 30*3<br>0     | 105           | 6            | 20                      | 108                  | 8.4           | 57         |  |  |  |

| [7]<br>2022                         | 110 FSI         | Yes                          | 22.4*<br>22.4 | 32            | 33           | 303                     | 12                   | 85            | 51         |  |  |  |

| [8]<br>2016                         | 110 FSI         | Yes                          | 11.2*<br>5.6  | N/R           | 10           | 200                     | 15                   | >167          | 30         |  |  |  |

| This<br>Work<br>2022                | 180 FSI         | No                           | 52.8*<br>52.8 | 138           | 8            | >20                     | 108                  | 5.6           | >62        |  |  |  |

Table 2. Performance comparison between SOAs